Logic Design Lab Experiments Dr. Manal Tantawi

|    | Experiment Title                          |

|----|-------------------------------------------|

| 1  | Logic gates                               |

| 2  | combination circuit I                     |

| 3  | Combination circuit II                    |

| 4  | Implementing functions using NAND only    |

| 5  | Implementing functions using NOR only     |

| 6  | Full adder                                |

| 7  | Full adder using decoder                  |

| 8  | Implementing functions using multiplexers |

| 9  | Sequential circuit                        |

| 10 | 2 bit counter                             |

| 11 | Pseudo-random generator                   |

| 12 | Frequency division                        |

### Lab 1 (logic gates)

**Objective:** introducing lab equipment and integrated circuits (ICs) to students.

Task to do in lab: verify truth table of logic gates.

### **OR gate (IC:7432)**

| X | Y | X+Y |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

#### AND gate (IC:7408)

| 0 | · · | /   |

|---|-----|-----|

| Х | Y   | X.Y |

| 0 | 0   | 0   |

| 0 | 1   | 0   |

| 1 | 0   | 0   |

| 1 | 1   | 1   |

### NOR gate (IC:7402)

| X | Y | (X+Y) <b>'</b> |

|---|---|----------------|

| 0 | 0 | 1              |

| 0 | 1 | 0              |

| 1 | 0 | 0              |

| 1 | 1 | 0              |

#### NAND gate (IC:7400)

| - <b>-</b> | - ( |        |

|------------|-----|--------|

| Х          | Y   | (X.Y)' |

| 0          | 0   | 1      |

| 0          | 1   | 1      |

| 1          | 0   | 1      |

| 1          | 1   | 0      |

### ICs for logic gates

# Lab 2 (combinational circuit I)

**Objective:** implementing simple combinational circuit.

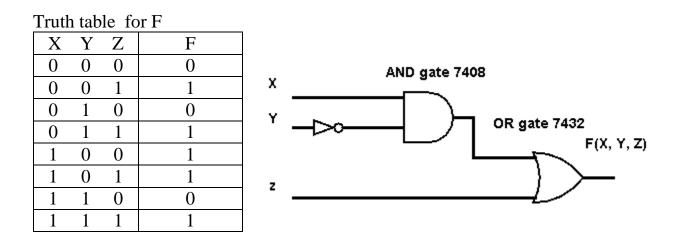

Task to do in lab: implementing practically the following function

F(X, Y, Z) = XY'+Z

### Lab 3 (combinational circuit II)

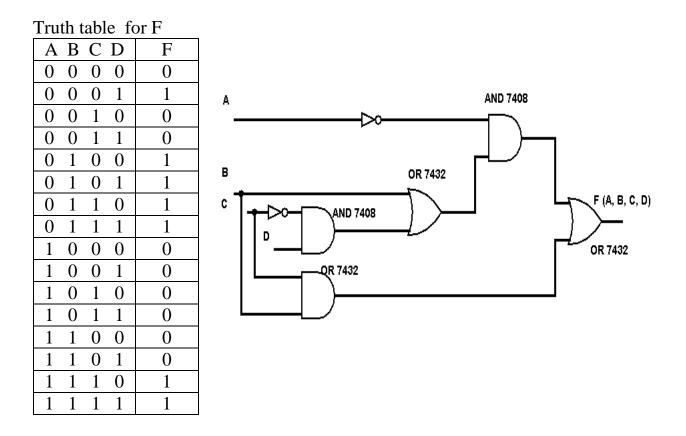

**Objective:** implementing combinational circuit (long expression)

Task to do in lab: implementing practically the following function

F(A, B, C, D) = A'(B + C'D) + BC

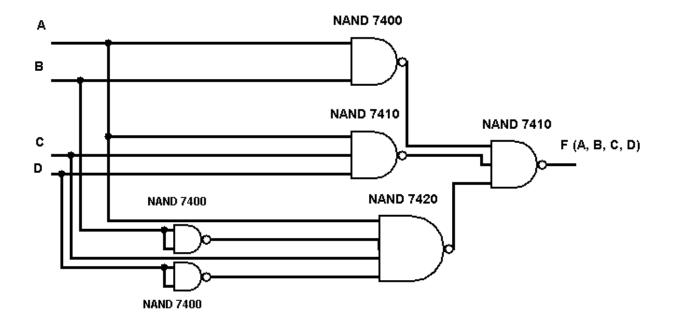

# Lab 4 (NAND only)

**Objective:** implementing Functions using NAND only

**Task to do in lab:** implementing practically the following function using NAND only

F(A, B, C, D) = AB + ACD + AB'CD'

F ( A, B, C, D) =  $\sum$ (10, 11, 12, 13, 14, 15)

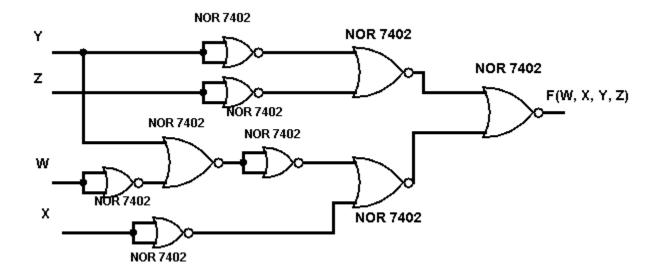

# Lab 5 (NOR only)

**Objective:** implementing functions using NOR only.

**Task to do in lab:** implementing practically the following function using NOR only.

F(W, X, Y, Z) = (Y'+Z')(W'+X'+Y)

$F(W, X, Y, Z) = \sum (0, 1, 2, 4, 5, 6, 8, 9, 10, 14)$

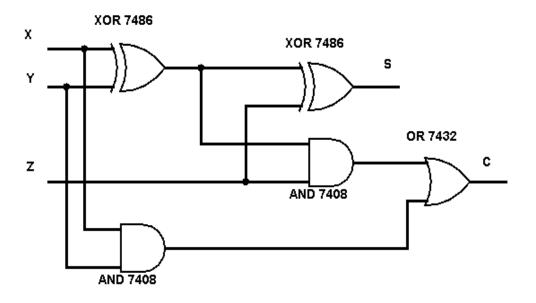

# Lab 6 (Full adder)

**Objective:** implementing Full Adder.

Task to do in lab: implementing practically the Full Adder.

| C S |

|-----|

| 0 0 |

| 0 1 |

| 0 1 |

| 1 0 |

| 0 1 |

| 1 0 |

| 1 0 |

| 1 1 |

|     |

Truth table for Full Adder

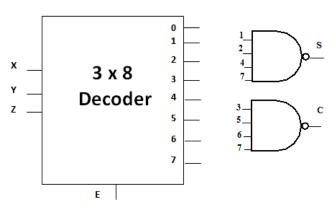

### Lab 7 (Decoders)

**Objective:** implementing functions using decoder.

**Task to do in lab:** implementing practically the Full Adder using suitable decoder.

Truth table for Full Adder

| X | Y | Ζ | C S |

|---|---|---|-----|

| 0 | 0 | 0 | 0 0 |

| 0 | 0 | 1 | 0 1 |

| 0 | 1 | 0 | 0 1 |

| 0 | 1 | 1 | 1 0 |

| 1 | 0 | 0 | 0 1 |

| 1 | 0 | 1 | 1 0 |

| 1 | 1 | 0 | 1 0 |

| 1 | 1 | 1 | 1 1 |

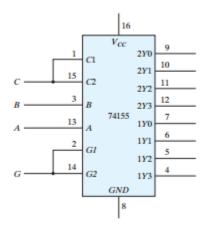

Full adder using active low decoder

Pin assignment for available Active low decoder IC: 74155 Truth table for IC: 74155

|   |     |      |   |     | Truth | table |     |      |              |     |          |

|---|-----|------|---|-----|-------|-------|-----|------|--------------|-----|----------|

|   | Inj | outs |   |     |       |       | Out | puts |              |     |          |

| G | С   | В    | Α | 2Y0 | 2Y1   | 2¥2   | 2¥3 | 1¥0  | 1 <b>Y</b> 1 | 172 | $1Y_{2}$ |

| 1 | х   | х    | х | 1   | 1     | 1     | 1   | 1    | 1            | 1   | 1        |

| 0 | 0   | 0    | 0 | 0   | 1     | 1     | 1   | 1    | 1            | 1   | 1        |

| 0 | 0   | 0    | 1 | 1   | 0     | 1     | 1   | 1    | 1            | 1   | 1        |

| 0 | 0   | 1    | 0 | 1   | 1     | 0     | 1   | 1    | 1            | 1   | 1        |

| 0 | 0   | 1    | 1 | 1   | 1     | 1     | 0   | 1    | 1            | 1   | 1        |

| 0 | 1   | 0    | 0 | 1   | 1     | 1     | 1   | 0    | 1            | 1   | 1        |

| 0 | 1   | 0    | 1 | 1   | 1     | 1     | 1   | 1    | 0            | 1   | 1        |

| 0 | 1   | 1    | 0 | 1   | 1     | 1     | 1   | 1    | 1            | 0   | 1        |

| 0 | 1   | 1    | 1 | 1   | 1     | 1     | 1   | 1    | 1            | 1   | 0        |

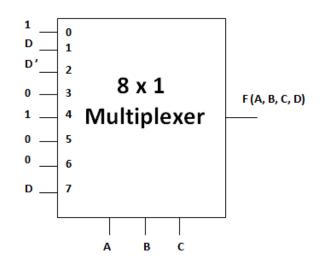

# Lab 8 (Multiplexers)

**Objective:** implementing functions using multiplexer.

**Task to do in lab**: implementing practically the Following function using multiplexer.

$F(A, B, C, D) = \sum (0, 1, 3, 4, 8, 9, 15)$

| Truth | n ta | ble | for | F |

|-------|------|-----|-----|---|

| Α     | В    | С   | D   | F |

| 0     | 0    | 0   | 0   | 1 |

| 0     | 0    | 0   | 1   | 1 |

| 0     | 0    | 1   | 0   | 0 |

| 0     | 0    | 1   | 1   | 1 |

| 0     | 1    | 0   | 0   | 1 |

| 0     | 1    | 0   | 1   | 0 |

| 0     | 1    | 1   | 0   | 0 |

| 0     | 1    | 1   | 1   | 0 |

| 1     | 0    | 0   | 0   | 1 |

| 1     | 0    | 0   | 1   | 1 |

| 1     | 0    | 1   | 0   | 0 |

| 1     | 0    | 1   | 1   | 0 |

| 1     | 1    | 0   | 0   | 0 |

| 1     | 1    | 0   | 1   | 0 |

| 1     | 1    | 1   | 0   | 0 |

| 1     | 1    | 1   | 1   | 1 |

Implementation using multiplexer

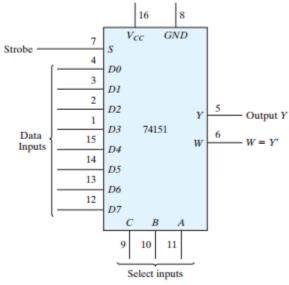

# Pin assignment for available multiplexer IC: 74151

#### Function table for IC: 74155

| Strobe |   | Select |   | Output |

|--------|---|--------|---|--------|

| S      | С | B      | A | Y      |

| 1      | х | х      | х | 0      |

| 0      | 0 | 0      | 0 | D0     |

| 0      | 0 | 0      | 1 | D1     |

| 0      | 0 | 1      | 0 | D2     |

| 0      | 0 | 1      | 1 | D3     |

| 0      | 1 | 0      | 0 | D4     |

| 0      | 1 | 0      | 1 | D5     |

| 0      | 1 | 1      | 0 | D6     |

| 0      | 1 | 1      | 1 | D7     |

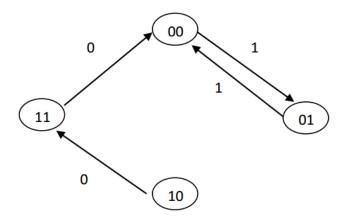

# Lab 9 (Sequential circuits)

**Objective:** implementing sequential circuits using different flip flops.

**Task to do in lab:** design and implement a sequential circuit that follows the following state diagram with one external output using T flip flops.

| A <sub>n</sub> | B <sub>n</sub> | $A_{n+1}$ | <b>B</b> <sub>n+1</sub> | T <sub>A</sub> | T <sub>B</sub> | Y |

|----------------|----------------|-----------|-------------------------|----------------|----------------|---|

| 0              | 0              | 0         | 1                       | 0              | 1              | 1 |

| 0              | 1              | 0         | 0                       | 0              | 1              | 1 |

| 1              | 0              | 1         | 1                       | 0              | 1              | 0 |

| 1              | 1              | 0         | 0                       | 1              | 1              | 0 |

$T_A = AB$   $T_B = 1$  Y = A'

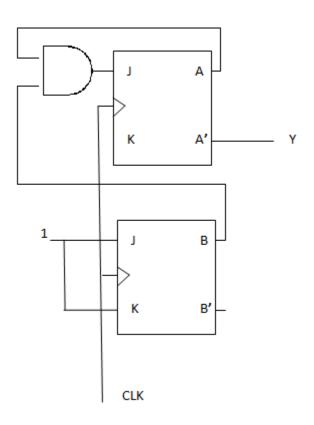

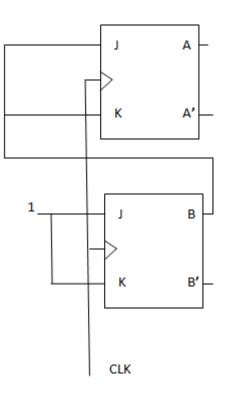

Circuit Logic diagram using JK flip flops ( j and k are connected to form T flip flop)

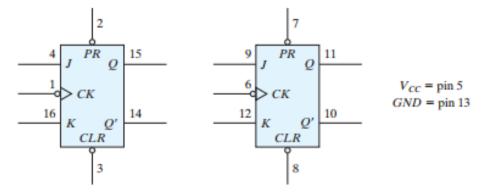

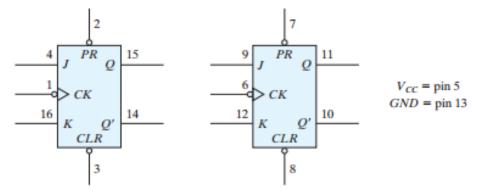

Pin assignment for available JK flip flop IC: 7476

|                  |                  | Inputs      |                  |                  | Out         | puts                    |

|------------------|------------------|-------------|------------------|------------------|-------------|-------------------------|

| Preset           | Clear            | Clock       | J                | K                | Q           | Q'                      |

| 0<br>1<br>0      | 1<br>0<br>0      | X<br>X<br>X | X<br>X<br>X      | x<br>x<br>x      | 1<br>0<br>1 | 0<br>1<br>1             |

| 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | Â           | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>1      | hange<br>1<br>0<br>ggle |

Function table

# Lab 10 (Counters)

**Objective:** implementing counter circuits using different flip flops.

**Task to do in lab**: design and implement a two bit counter using JK flipflops

| A <sub>n</sub> | B <sub>n</sub> | A <sub>n+1</sub> | B <sub>n+1</sub> | JA | K <sub>B</sub> | J <sub>B</sub> | K <sub>B</sub> |

|----------------|----------------|------------------|------------------|----|----------------|----------------|----------------|

| 0              | 0              | 0                | 1                | 0  | Х              | 1              | Х              |

| 0              | 1              | 1                | 0                | 1  | Х              | Х              | 1              |

| 1              | 0              | 1                | 1                | Х  | 0              | 1              | Х              |

| 1              | 1              | 0                | 0                | Х  | 1              | Х              | 1              |

$\begin{aligned} J_A &= K_A = B\\ J_B &= K_B = 1 \end{aligned}$

Circuit Logic diagram using JK flip flops

Pin assignment for available JK flip flop IC: 7476

Function table

|                  | Outputs          |             |                  |                  |             |                         |

|------------------|------------------|-------------|------------------|------------------|-------------|-------------------------|

| Preset           | Clear            | Clock       | J                | K                | Q           | Qʻ                      |

| 0<br>1<br>0      | 1<br>0<br>0      | X<br>X<br>X | X<br>X<br>X      | x<br>x<br>x      | 1<br>0<br>1 | 0<br>1<br>1             |

| 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 |             | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>1      | hange<br>1<br>0<br>ggle |

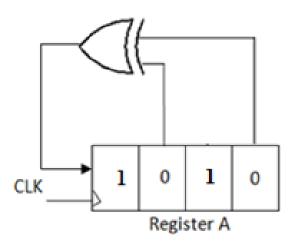

# Lab 11 (Registers)

**Objective:** implementing pseudorandom generator using 4 bit shift register.

**Task to do in lab:** use 4 bit shift register with XOR to generate random numbers.

| Serial input (SI) | Register Content |

|-------------------|------------------|

| 0                 | 1010             |

| 0                 | 0101             |

| 0                 | 0010             |

| 1                 | 0001             |

| 0                 | 1000             |

| 1                 | 0100             |

|                   | 1010             |

#### Cycle length = 6

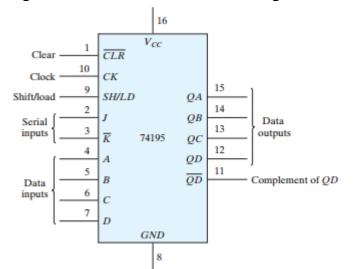

### Pin assignment for available 4 bit shift register IC: 74195

| - HOUR | oction | tabl | 10 |

|--------|--------|------|----|

| 1.01   | iciion | Laur | -  |

| Clear                 | Shift/<br>load        | Clock            | J                | ĸ                | Serial<br>input  | Function                                                                                                                                         |

|-----------------------|-----------------------|------------------|------------------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>1<br>1<br>1 | X<br>X<br>0<br>1<br>1 | X<br>0<br>↑<br>↑ | X<br>X<br>0<br>1 | X<br>X<br>0<br>1 | X<br>X<br>0<br>1 | Asynchronous clear<br>No change in output<br>Load input data<br>Shift from $QA$ toward $QD$ , $QA = 0$<br>Shift from $QA$ toward $QD$ , $QA = 1$ |

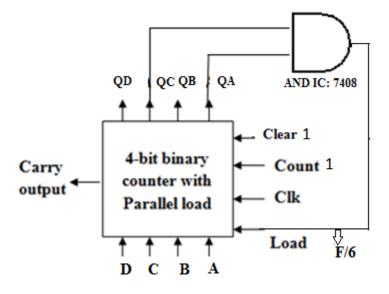

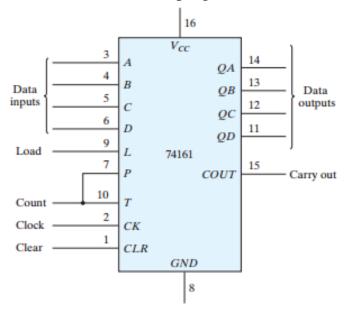

### Lab 12 (Programmable counters)

**Objective:** implementing frequency divider.

**Task to do in lab:** implement frequency divider using 4 bit programmable counter. Ex: F/6

Pin assignment for available 4 bit programmable counter IC: 74161

| Function | table |  |

|----------|-------|--|

|----------|-------|--|

| Clear            | Clock       | Load             | Count            | Function                                                                                   |

|------------------|-------------|------------------|------------------|--------------------------------------------------------------------------------------------|

| 0<br>1<br>1<br>1 | X<br>↑<br>↑ | X<br>0<br>1<br>1 | X<br>X<br>1<br>0 | Clear outputs to 0<br>Load input data<br>Count to next binary value<br>No change in output |