#### Lecture 6:

Chapter 4: Combinational Logic

Mirvat Al-Qutt, Ph.D Computer Systems Department , FCIS, Ain Shams University

# **Design Procedure**

2

- Input: the specification of the problem.

- Output: the logic circuit diagram or Boolean functions.

- **derive the truth table** that defines the required relationship between inputs and outputs

- obtain the **simplified Boolean function** for each output as a function of the input variables

- draw the logic diagram and verify the correctness of the design.

### **Code Conversion Design Problems**

- It is sometimes necessary to use the output of one system as the input to another.

- A conversion circuit must be inserted between the two system if each uses different codes for the same information.

- Thus, a code converter is a circuit that makes the two system compatible even though each uses a different binary code.

- To convert from binary code A to binary code B, the input lines must supply the bit combination of elements as specified by code A and the output lines must generate the corresponding bit combination of code B.

#### BCD to Excess-3 Code Converter

|                      |   | Input | BCD |   | Output Excess-3 Code |   |   |   |

|----------------------|---|-------|-----|---|----------------------|---|---|---|

|                      | А | В     | С   | D | w                    | х | у | z |

| Input BCD            | 0 | 0     | 0   | 0 | 0                    | 0 | 1 | 1 |

| 4 – Variables Input  | 0 | 0     | 0   | 1 | 0                    | 1 | 0 | 0 |

| Output Excess-3      | 0 | 0     | 1   | 0 | 0                    | 1 | 0 | 1 |

| 4 – Variables output | 0 | 0     | 1   | 1 | 0                    | 1 | 1 | 0 |

|                      | 0 | 1     | 0   | 0 | 0                    | 1 | 1 | 1 |

|                      | 0 | 1     | 0   | 1 | 1                    | 0 | 0 | 0 |

|                      | 0 | 1     | 1   | 0 | 1                    | 0 | 0 | 1 |

|                      | 0 | 1     | 1   | 1 | 1                    | 0 | 1 | 0 |

|                      | 1 | 0     | 0   | 0 | 1                    | 0 | 1 | 1 |

|                      | 1 | 0     | 0   | 1 | 1                    | 1 | 0 | 0 |

# **Code Conver**

- BCD to Excess-3 Code Converter

- Input BCD

- 4 Variables Input

- Output Excess-3

- 4 Variables output

|   | Input BCD- Code |   |   |   | Output Excess -3 Code |   |   |   |  |

|---|-----------------|---|---|---|-----------------------|---|---|---|--|

|   | Α               | В | С | D | W                     | Х | Y | Z |  |

| - | 0               | 0 | 0 | 0 | 0                     | 0 |   | I |  |

|   | 0               | 0 | 0 | I | 0                     | I | 0 | 0 |  |

|   | 0               | 0 | I | 0 | 0                     | I | 0 | I |  |

|   | 0               | 0 | I | I | 0                     | I | I | 0 |  |

|   | 0               | I | 0 | 0 | 0                     | I | I | I |  |

|   | 0               | I | 0 | I | I                     | 0 | 0 | 0 |  |

|   | 0               | I | I | 0 | I                     | 0 | 0 | I |  |

|   | 0               | I | I | I | I                     | 0 | I | 0 |  |

|   | I               | 0 | 0 | 0 | I                     | 0 | I | I |  |

|   | I               | 0 | 0 |   | I                     | I | 0 | 0 |  |

|   | I.              | 0 | 1 | 0 | x                     | x | x | x |  |

|   | I.              | 0 | 1 | 1 | x                     | x | x | x |  |

|   | I.              | 1 | 0 | 0 | x                     | x | x | x |  |

|   | L               | I | 0 | I | x                     | х | х | x |  |

|   | I.              | 1 | 1 | 0 | x                     | x | x | x |  |

|   | I.              | 1 | 1 | 1 | x                     | x | x | x |  |

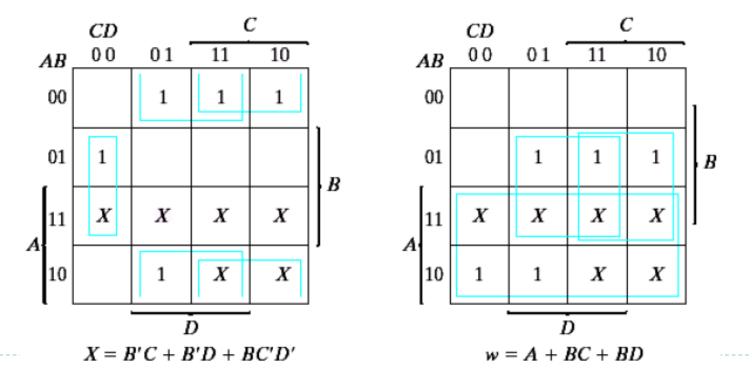

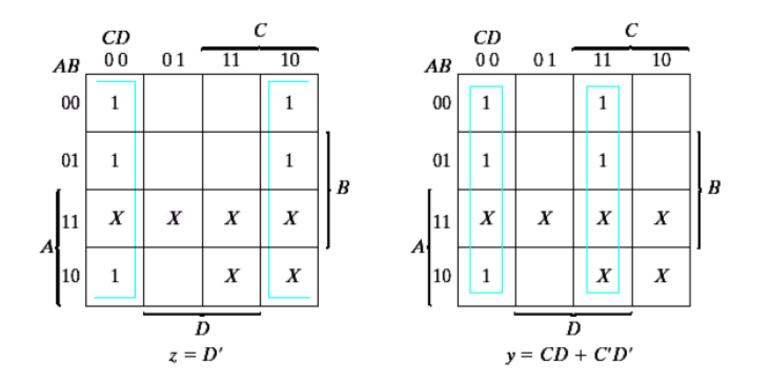

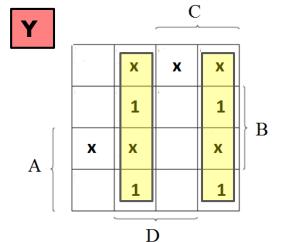

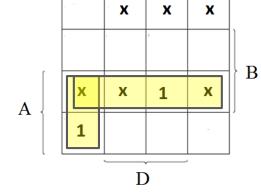

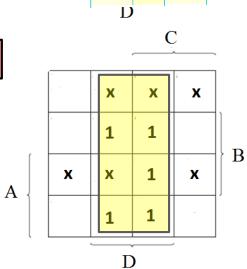

- Boolean Expression :

- The six don't care minterms (10~15) are marked with X.

- Each of four maps represents one of the four outputs of this circuit as a function of the four input variables.

Boolean Expression : (

Þ

3

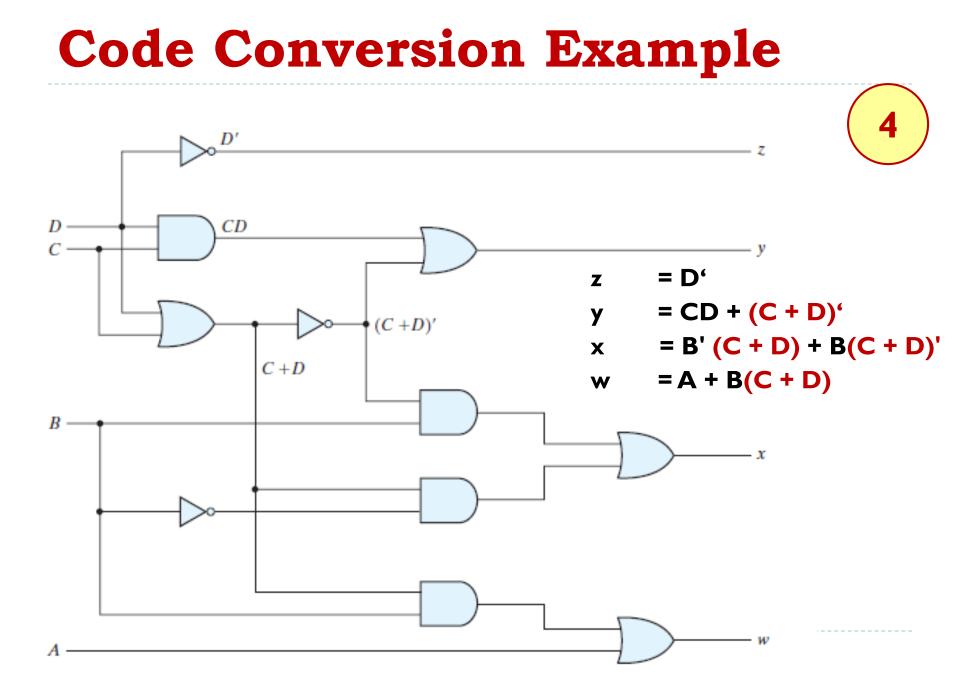

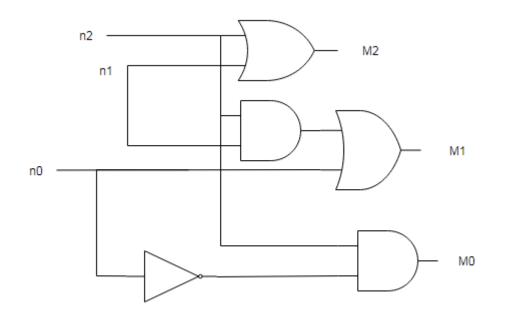

**Logic Diagram:** Reduce the number of gates used.

4

| Z | = D'                                          | Х | = B'C + B'D + BC' D'<br>= B' (C + D) + BC' D'<br>= B' (C + D) + B(C + D)' |

|---|-----------------------------------------------|---|---------------------------------------------------------------------------|

| у | = CD + C' D'<br>= CD + <mark>(C + D)</mark> ' | w | = A + BC + BD<br>= A + B <mark>(C + D)</mark>                             |

#### C + D is used to implement the three outputs.

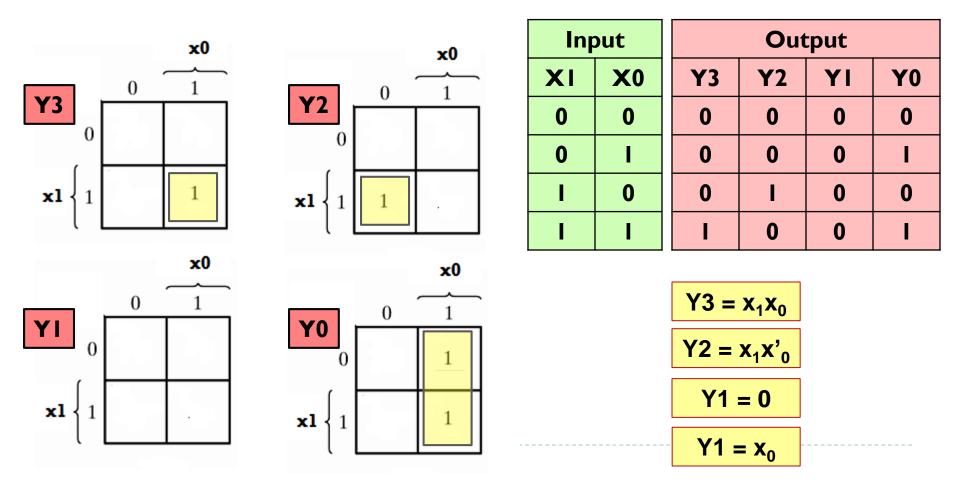

Design a circuit that takes an input X = x<sub>1</sub> x<sub>0</sub> and calculate the output Y = X<sup>2</sup>

Design a circuit that takes an input X = x<sub>1</sub> x<sub>0</sub> and calculate the output Y = X<sup>2</sup>

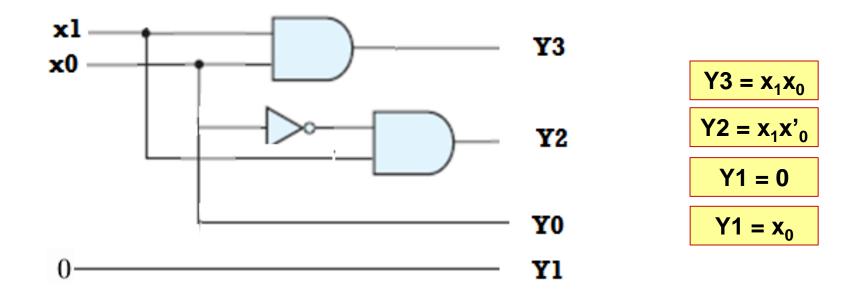

Design a circuit that takes an input N = n<sub>2</sub> n<sub>1</sub> n<sub>0</sub> and calculates the output M, where M is calculated as the following:

$$M = \begin{cases} 2N & 0 \le N \le 3\\ N+1 & 4 \le N < 7 \end{cases}$$

| Input |    |    | Output |    |    |  |

|-------|----|----|--------|----|----|--|

| n2    | nl | n0 | M2     | MI | M0 |  |

| 0     | 0  | 0  | 0      | 0  | 0  |  |

| 0     | 0  | I  | 0      | I  | 0  |  |

| 0     | I  | 0  | I      | 0  | 0  |  |

| 0     | I  | I  | I      | I  | 0  |  |

| I     | 0  | 0  | I      | 0  | I  |  |

| I     | 0  | I  | I      | I  | 0  |  |

| I     | I  | 0  | I      | I  | I  |  |

| I     | I  |    | x      | x  | x  |  |

Design a circuit that takes an input N = n<sub>2</sub> n<sub>1</sub> n<sub>0</sub> and calculates the output M, where M is calculated as the following:

$$M = \begin{cases} 2N & 0 \le N \le 3 \\ N+1 & 4 \le N \le 7 \end{cases}$$

| Output |          |   |  |  |  |  |  |

|--------|----------|---|--|--|--|--|--|

| M2     | M2 MI M0 |   |  |  |  |  |  |

| 0      | 0        | 0 |  |  |  |  |  |

| 0      | I        | 0 |  |  |  |  |  |

| I      | 0        | 0 |  |  |  |  |  |

| I      | I        | 0 |  |  |  |  |  |

| I      | 0        | Ι |  |  |  |  |  |

| I      | I        | 0 |  |  |  |  |  |

| Ι      | Ι        | Ι |  |  |  |  |  |

| x      | x        | x |  |  |  |  |  |

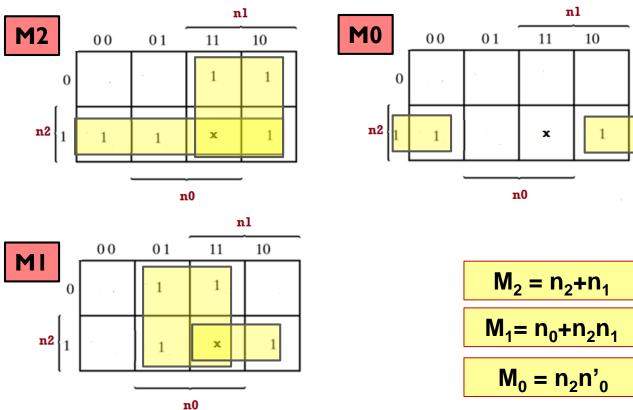

Design a circuit that takes an input N = n<sub>2</sub> n<sub>1</sub> n<sub>0</sub> and calculates the output M, where M is calculated as the following:

$$M = \begin{cases} 2N & 0 \le N \le 3\\ N+1 & 4 \le N < 7 \end{cases}$$

$$M_2 = n_2 + n_1$$

$M_1 = n_0 + n_2 n_1$

$M_0 = n_2 n_0'$

Table 1.5

#### Design a code converter that converts a decimal digit from, The 8, 4, -2, -1 code to BCD

Four Different Binary Codes for the Decimal Digits

| Decimal<br>Digit | BCD<br>8421 | 2421 | Excess-3 | 8, 4, -2, -1 |

|------------------|-------------|------|----------|--------------|

| 0                | 0000        | 0000 | 0011     | 0000         |

| 1                | 0001        | 0001 | 0100     | 0111         |

| 2                | 0010        | 0010 | 0101     | 0110         |

| 3                | 0011        | 0011 | 0110     | 0101         |

| 4                | 0100        | 0100 | 0111     | 0100         |

| 5                | 0101        | 1011 | 1000     | 1011         |

| 6                | 0110        | 1100 | 1001     | 1010         |

| 7                | 0111        | 1101 | 1010     | 1001         |

| 8                | 1000        | 1110 | 1011     | 1000         |

| 9                | 1001        | 1111 | 1100     | 1111         |

|                  | 1010        | 0101 | 0000     | 0001         |

| Unused           | 1011        | 0110 | 0001     | 0010         |

| bit              | 1100        | 0111 | 0010     | 0011         |

| combi-           | 1101        | 1000 | 1101     | 1100         |

| nations          | 1110        | 1001 | 1110     | 1101         |

|                  | 1111        | 1010 | 1111     | 1110         |

Design a code converter that converts a decimal digit from, The 8, 4, -2, -1 code to BCD

| BCD<br>8421 | 8, 4, -2, -1 |

|-------------|--------------|

| 0000        | 0000         |

| 0001        | 0111         |

| 0010        | 0110         |

| 0011        | 0101         |

| 0100        | 0100         |

| 0101        | 1011         |

| 0110        | 1010         |

| 0111        | 1001         |

| 1000        | 1000         |

| 1001        | 1111         |

| 1010        | 0001         |

| 1011        | 0010         |

| 1100        | 0011         |

| 1101        | 1100         |

| 1110        | 1101         |

| 1111        | 1110         |

| Input 8, 4, −2, −1 code |   |    |   | Output BCD |   |   |   |  |

|-------------------------|---|----|---|------------|---|---|---|--|

| Α                       | В | C  | D | W          | X | Y | Z |  |

| 0                       | 0 | 0  | 0 | 0          | 0 | 0 | 0 |  |

| 0                       | 0 | 0  |   | X          | X | X | X |  |

| 0                       | 0 | 1  | 0 | X          | X | X | x |  |

| 0                       | 0 | 1  | 1 | X          | X | X | x |  |

| 0                       | I | 0  | 0 | 0          | I | 0 | 0 |  |

| 0                       | I | 0  | I | 0          | 0 | I | Ι |  |

| 0                       | I | I  | 0 | 0          | 0 | I | 0 |  |

| 0                       | I | I  | I | 0          | 0 | 0 | I |  |

| I                       | 0 | 0  | 0 | I          | 0 | 0 | 0 |  |

| I                       | 0 | 0  |   | 0          | I |   | I |  |

| I                       | 0 | I  | 0 | 0          | I | l | 0 |  |

| I                       | 0 | I  | I | 0          | I | 0 | Ι |  |

| 1                       | 1 | 0  | 0 | X          | X | X | X |  |

| 1                       | 1 | 0  | 1 | X          | X | X | X |  |

| 1                       | 1 | 1  | 0 | X          | X | X | X |  |

| I                       | I | I. | I | I          | 0 | 0 | I |  |

W = AB + AC'D' X = B'C + B'D + B'C'D' Y = CD' + C'D Z = D

W

С

Χ

Ζ

С

|   | Output BCD |   |   |  |  |  |  |  |

|---|------------|---|---|--|--|--|--|--|

| W | X Y Z      |   |   |  |  |  |  |  |

| 0 | 0          | 0 | 0 |  |  |  |  |  |

| X | X          | X | X |  |  |  |  |  |

| X | X          | X | X |  |  |  |  |  |

| X | X          | X | X |  |  |  |  |  |

| 0 |            | 0 | 0 |  |  |  |  |  |

| 0 | 0          |   | I |  |  |  |  |  |

| 0 | 0          | I | 0 |  |  |  |  |  |

| 0 | 0          | 0 |   |  |  |  |  |  |

| Ι | 0          | 0 | 0 |  |  |  |  |  |

| 0 | I          | Ι | Ι |  |  |  |  |  |

| 0 | I          | I | 0 |  |  |  |  |  |

| 0 | I          | 0 | I |  |  |  |  |  |

| X | X          | X | X |  |  |  |  |  |

| X | X          | X | X |  |  |  |  |  |

| X | X          | X | X |  |  |  |  |  |

| I | 0          | 0 | I |  |  |  |  |  |

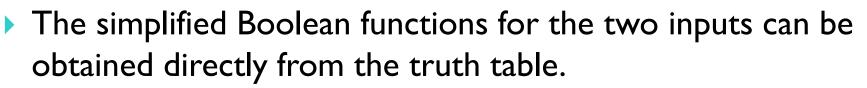

# Adder

- The most basic arithmetic operation is the addition of two binary digits

- When both augend and addend bits are equal to 1, the binary sum consists of two digits (1 + 1 = 10)

- The higher significant bit of this result is called a <u>carry</u>

- A combination circuit that performs the addition of two bits is <u>half adder</u>.

- A adder performs the addition of three bits (2 significant bits and a previous carry) is called a <u>full adder</u>

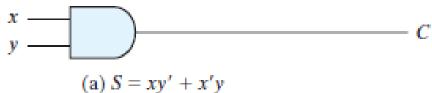

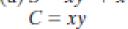

# Half Adder

- Inputs: x and y

- **Outputs**: S (for sum) and C (for carry)

## Half Adder

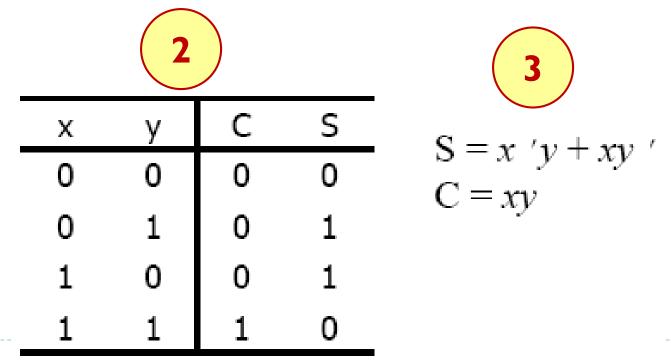

## **Implementation of Half Adder**

Þ

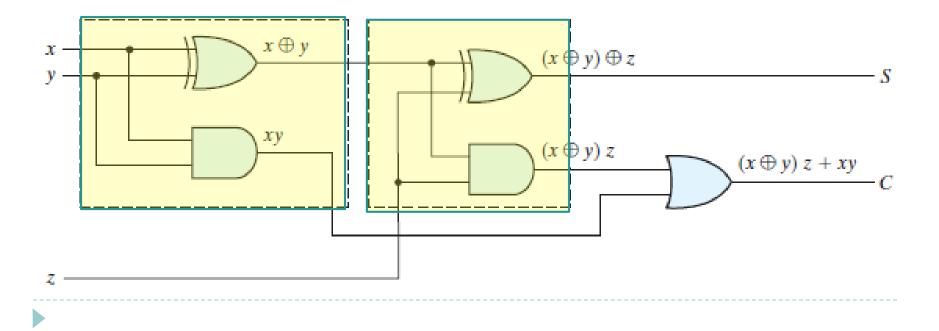

### **Full Adder**

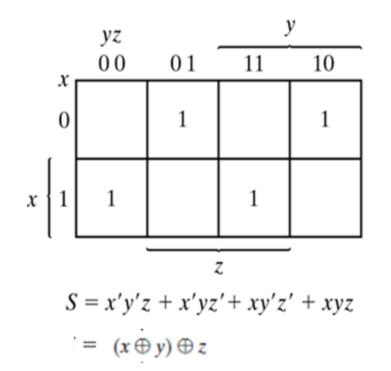

# **Full Adder**

A full adder is a combinational circuit that forms the arithmetic sum of three input bits

It consists of three inputs and two outputs.

| Full Ac | lder | 2 |   |   |

|---------|------|---|---|---|

| x       | y    | z | C | S |

| 0       | 0    | 0 | 0 | 0 |

| 0       | 0    | 1 | 0 | 1 |

| 0       | 1    | 0 | 0 | 1 |

| 0       | 1    | 1 | 1 | 0 |

| 1       | 0    | 0 | 0 | 1 |

| 1       | 0    | 1 | 1 | 0 |

| 1       | 1    | 0 | 1 | 0 |

| 1       | 1    | 1 | 1 | 1 |

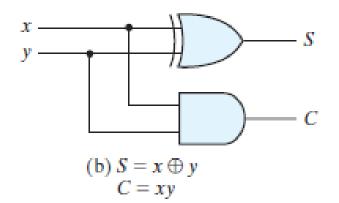

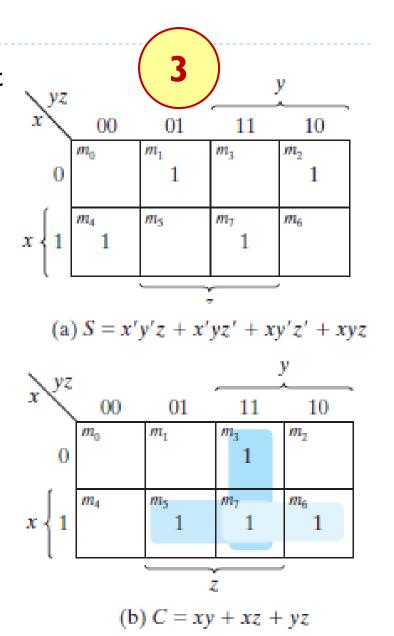

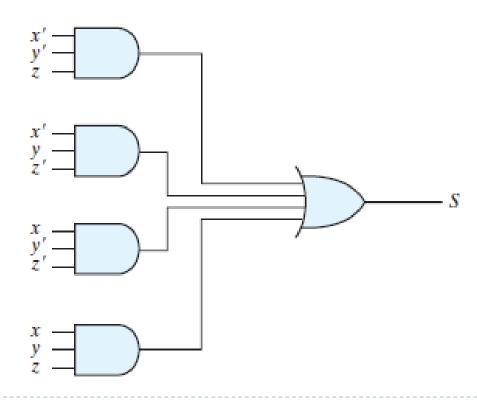

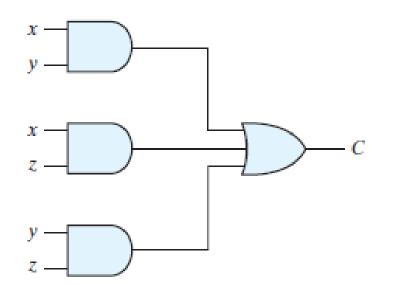

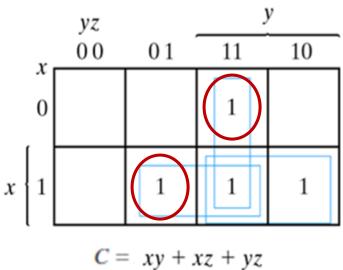

# **Implementation of Full Adder**

(a)

$$S = x'y'z + x'yz' + xy'z' + xyz$$

(b) C = xy + xz + yz

# **Full Adder**

- A full adder is a combinational circuit that forms the arithmetic sum of three input bits 2

- It consists of three inputs and two outputs.

D

= xy + xy'z + x'yz $= xy + (x \oplus y)z$

# **Implementation of Full Adder**

A full adder can be implemented with two half adders and an OR gate

$$S = x'y'z + x'yz' + xy'z' + xyz$$

$$= (x \oplus y) \oplus z$$

$$C = xy + xz + yz$$

=  $xy + xy'z + x'yz$

=  $xy + (x \oplus y)z$

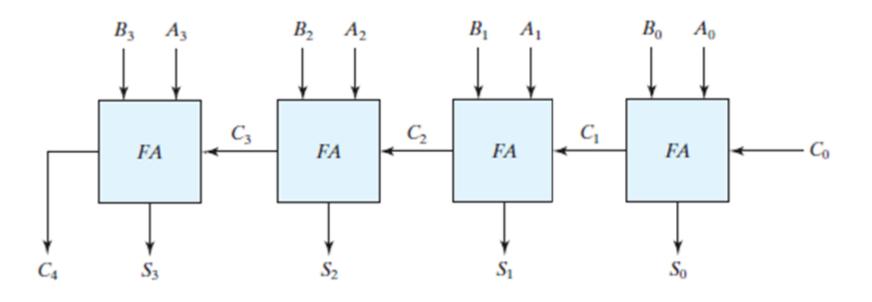

### **4 Bits Binary Parallel Adder**

# **Binary Parallel Adder**

- A binary adder produces the arithmetic sum of two binary numbers in parallel.

- Consider two binary number: A = 1011 and B = 0011

| Subscript i : | 3  | 2    | 1    | 0 |                  |

|---------------|----|------|------|---|------------------|

| Input carry   | 0+ |      |      | 0 | C                |

| Augend        | 1  | 0    | 1    | 1 | A <sub>i</sub>   |

| Addend        | 0  | 0    | 1    | 1 | Bi               |

| Sum           | 1  | 1    | 1    | 0 | Si               |

| Output carry  | 0  | -(0) | -(1) |   | C <sub>i+1</sub> |

- The output carry from each full adder is connected to input carry of the next full adder in the chain.

- An n-bit parallel adder requires n full-adder

- 4-bit adder: Interconnection of four full adder (FA) circuits.

## **4-bit Adder Example**

| Subscript i : | 3  | 2    | 1    | 0           |                  |

|---------------|----|------|------|-------------|------------------|

| Input carry   | 0+ |      |      | 0           | C                |

| Augend        | 1  | 0    | 1    | 1           | A                |

| Addend        | 0  | 0    | 1    | 1           | Bi               |

| Sum           | 1  | 1    | 1    | 0           | Si               |

| Output carry  | 0  | -(0) | -(1) | <u>(1</u> ) | C <sub>i+1</sub> |

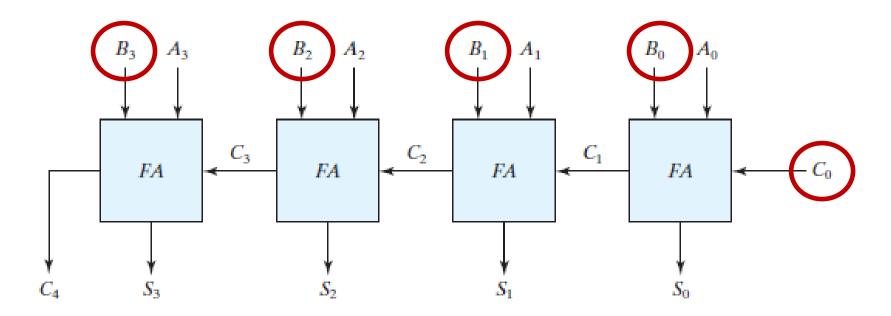

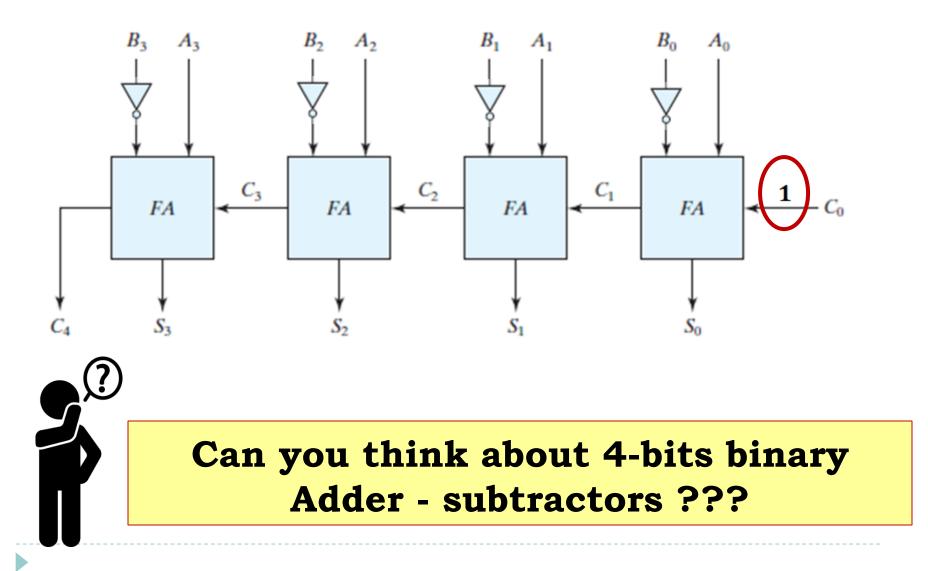

## **4-bit Binary Subtractor**

## **4-bit Adder Example**

# **4-bit Subtractor Example**

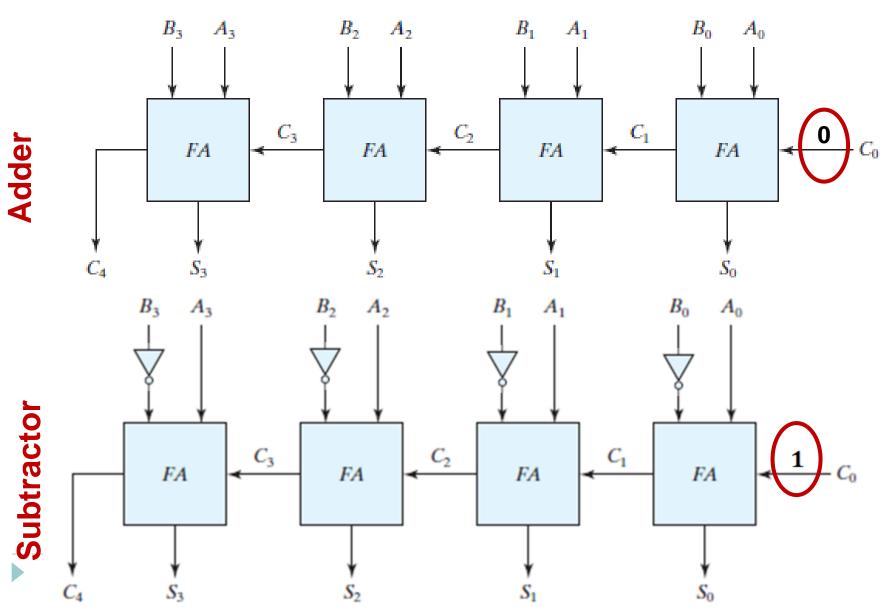

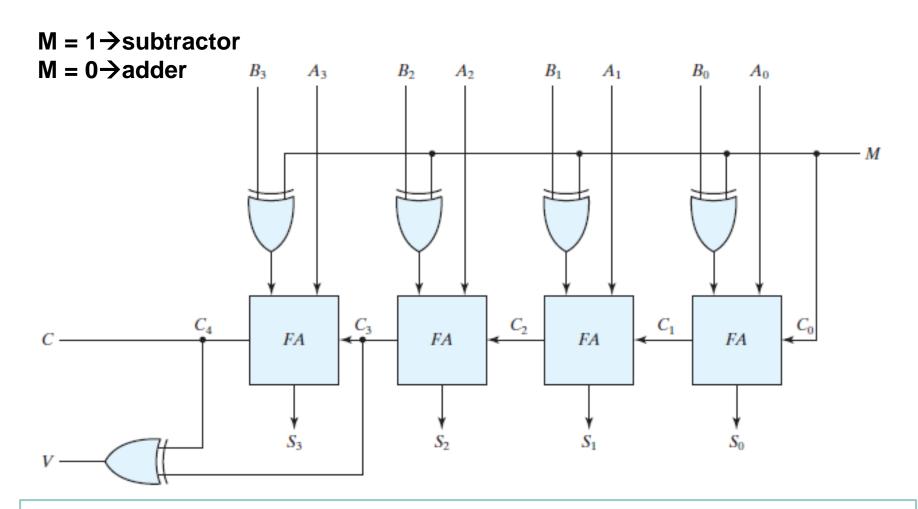

### **4-bit Adder-Subtractor**

#### **4-bit Adder-Subtractor**

| Function   | C <sub>0</sub> | Opr. |

|------------|----------------|------|

| Adder      | 0              | A+B  |

| Subtractor |                | A+B' |

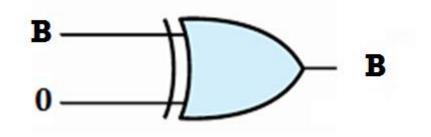

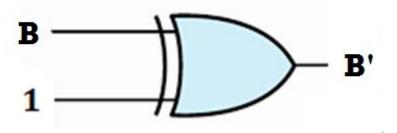

#### **Recall some XOR properties**

| XOR             | <b>B ⊕ 0 = B</b>          |

|-----------------|---------------------------|

| Some identities | <b>B</b> ⊕ I = <b>B</b> ' |

### **4-bit Adder-Subtractor Example**

**Overflow** is a problem in digital computers because the number of bits that hold the number is finite and a result that contains n+1 bits cannot be accommodated.

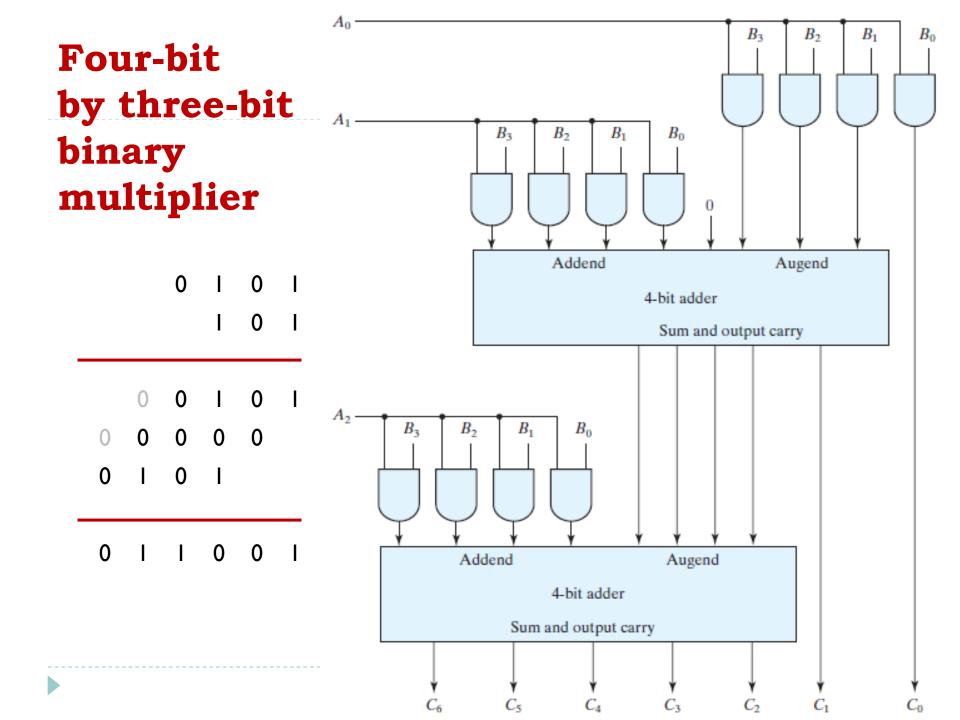

### **Binary Multiplier**

- Multiplication of binary numbers is performed in the same way as multiplication of decimal numbers.

- The multiplicand is multiplied by each bit of the multiplier, starting from the least significant bit.

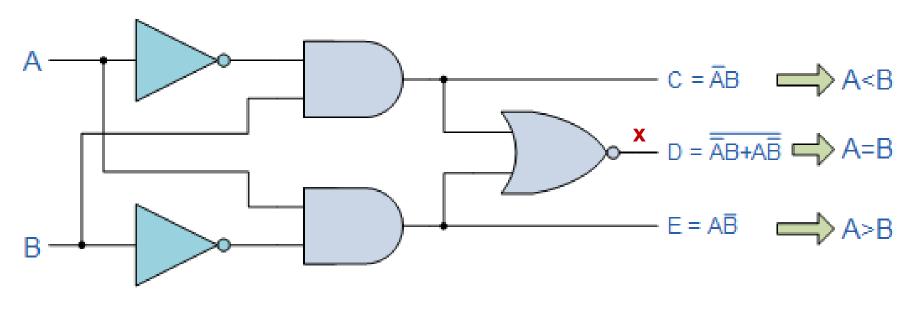

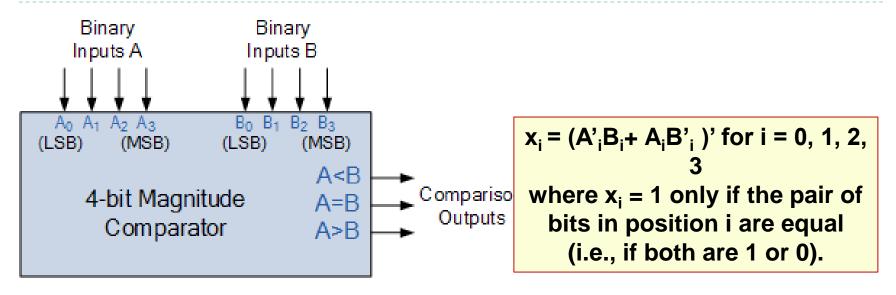

### **Magnitude Comparator**

- The comparison of two numbers is an operation that determines whether one number is greater than, less than, or equal to the other number.

- A magnitude comparator is a combinational circuit that compares two numbers A and B and determines their relative magnitudes.

- The outcome of the comparison is specified by three binary variables that indicate whether

- ► A > B,

- ▶ A = B, or

- ► A < B.

### **Magnitude Comparator**

| Α | В | A <b< th=""><th>A=B</th><th>A&gt;B</th></b<> | A=B | A>B |

|---|---|----------------------------------------------|-----|-----|

| 0 | 0 | 0                                            | I   | 0   |

| 0 | I | I                                            | 0   | 0   |

| I | 0 | 0                                            | 0   | I   |

| I | I | 0                                            | I   | 0   |

x = (A'B + A B')' where x= 1 only if the pair of bits A and B are equal

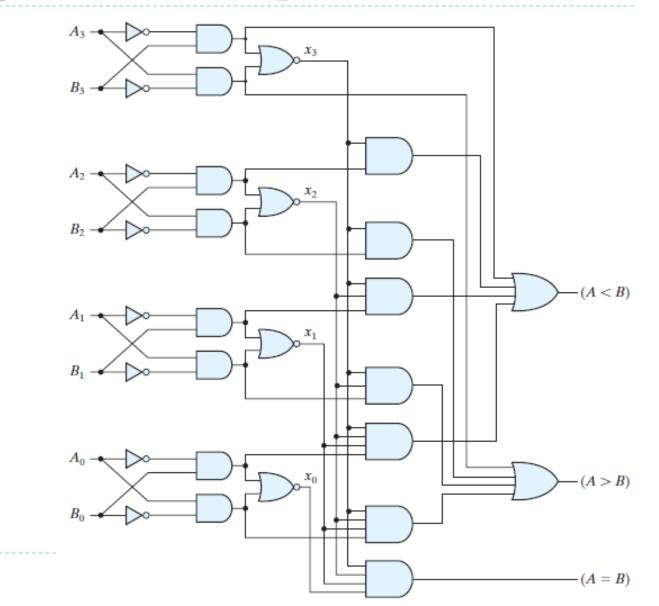

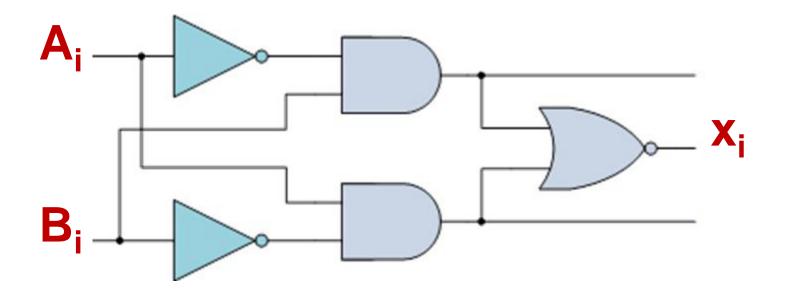

#### **Magnitude Comparator**

$$x_i = (A'_iB_i + A_iB'_i)$$

for  $i = 0, 1, 2, 3$

where  $x_i = 1$  only if the pair of bits in position i are equal (i.e., if both are 1 or 0).

#### **4 Bits Magnitude Comparator**

$(A = B) = x_3 x_2 x_1 x_0$

$(A > B) = A_{3}B'_{3} + x_{3}A_{2}B'_{2} + x_{3}x_{2}A_{1}B'_{1} + x_{3}x_{2}x_{1}A_{0}B'_{0}$

$(A < B) = A'_{3}B_{3} + x_{3}A'_{2}B_{2} + x_{3}x_{2}A'_{1}B_{1} + x_{3}x_{2}x_{1}A'_{0}B_{0}$

#### **4 Bits Magnitude Comparator**